|

Hanna

Sourcecode Batteriemanagementsystem |

|

|

Hanna

Sourcecode Batteriemanagementsystem |

|

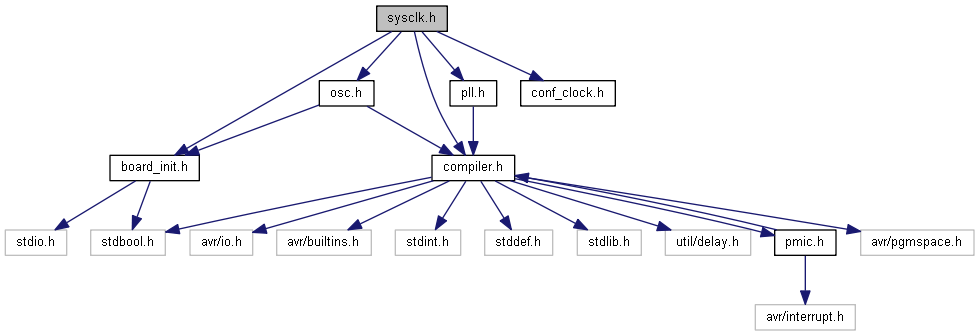

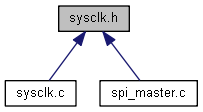

Chip-specific system clock management functions. Mehr ...

#include <board_init.h>#include <compiler.h>#include <osc.h>#include <pll.h>#include "conf_clock.h"

gehe zum Quellcode dieser Datei

Makrodefinitionen | |

System Clock Sources | |

| #define | SYSCLK_SRC_RC2MHZ CLK_SCLKSEL_RC2M_gc |

| Internal 2 MHz RC oscillator. | |

| #define | SYSCLK_SRC_RC32MHZ CLK_SCLKSEL_RC32M_gc |

| Internal 32 MHz RC oscillator. | |

| #define | SYSCLK_SRC_RC32KHZ CLK_SCLKSEL_RC32K_gc |

| Internal 32 KHz RC oscillator. | |

| #define | SYSCLK_SRC_XOSC CLK_SCLKSEL_XOSC_gc |

| External oscillator. | |

| #define | SYSCLK_SRC_PLL CLK_SCLKSEL_PLL_gc |

| Phase-Locked Loop. | |

Prescaler A Setting (relative to CLKsys) | |

| #define | SYSCLK_PSADIV_1 CLK_PSADIV_1_gc |

| Do not prescale. | |

| #define | SYSCLK_PSADIV_2 CLK_PSADIV_2_gc |

| Prescale CLKper4 by 2. | |

| #define | SYSCLK_PSADIV_4 CLK_PSADIV_4_gc |

| Prescale CLKper4 by 4. | |

| #define | SYSCLK_PSADIV_8 CLK_PSADIV_8_gc |

| Prescale CLKper4 by 8. | |

| #define | SYSCLK_PSADIV_16 CLK_PSADIV_16_gc |

| Prescale CLKper4 by 16. | |

| #define | SYSCLK_PSADIV_32 CLK_PSADIV_32_gc |

| Prescale CLKper4 by 32. | |

| #define | SYSCLK_PSADIV_64 CLK_PSADIV_64_gc |

| Prescale CLKper4 by 64. | |

| #define | SYSCLK_PSADIV_128 CLK_PSADIV_128_gc |

| Prescale CLKper4 by 128. | |

| #define | SYSCLK_PSADIV_256 CLK_PSADIV_256_gc |

| Prescale CLKper4 by 256. | |

| #define | SYSCLK_PSADIV_512 CLK_PSADIV_512_gc |

| Prescale CLKper4 by 512. | |

Prescaler B and C Setting (relative to CLKper4) | |

| #define | SYSCLK_PSBCDIV_1_1 CLK_PSBCDIV_1_1_gc |

| Do not prescale. | |

| #define | SYSCLK_PSBCDIV_1_2 CLK_PSBCDIV_1_2_gc |

| Prescale CLKper and CLKcpu by 2. | |

| #define | SYSCLK_PSBCDIV_4_1 CLK_PSBCDIV_4_1_gc |

| Prescale CLKper2, CLKper and CLKcpu by 4. | |

| #define | SYSCLK_PSBCDIV_2_2 CLK_PSBCDIV_2_2_gc |

| Prescale CLKper2 by 2, CLKper and CLKcpu by 4. | |

Clocks not associated with any port | |

| |

| #define | SYSCLK_DMA PR_DMA_bm |

| DMA Controller. | |

| #define | SYSCLK_EDMA PR_EDMA_bm |

| EDMA Controller. | |

| #define | SYSCLK_EVSYS PR_EVSYS_bm |

| Event System. | |

| #define | SYSCLK_RTC PR_RTC_bm |

| Real-Time Counter. | |

| #define | SYSCLK_EBI PR_EBI_bm |

| Ext Bus Interface. | |

| #define | SYSCLK_AES PR_AES_bm |

| AES Module. | |

| #define | SYSCLK_USB PR_USB_bm |

| USB Module. | |

| #define | SYSCLK_XCL PR_XCL_bm |

| USB Module. | |

Clocks on PORTA and PORTB | |

| |

| #define | SYSCLK_AC PR_AC_bm |

| Analog Comparator. | |

| #define | SYSCLK_ADC PR_ADC_bm |

| A/D Converter. | |

| #define | SYSCLK_DAC PR_DAC_bm |

| D/A Converter. | |

Clocks on PORTC, PORTD, PORTE and PORTF | |

| |

| #define | SYSCLK_TC0 PR_TC0_bm |

| Timer/Counter 0. | |

| #define | SYSCLK_TC1 PR_TC1_bm |

| Timer/Counter 1. | |

| #define | SYSCLK_TC4 PR_TC4_bm |

| Timer/Counter 0. | |

| #define | SYSCLK_TC5 PR_TC5_bm |

| Timer/Counter 1. | |

| #define | SYSCLK_HIRES PR_HIRES_bm |

| Hi-Res Extension. | |

| #define | SYSCLK_SPI PR_SPI_bm |

| SPI controller. | |

| #define | SYSCLK_USART0 PR_USART0_bm |

| USART 0. | |

| #define | SYSCLK_USART1 PR_USART1_bm |

| USART 1. | |

| #define | SYSCLK_TWI PR_TWI_bm |

| TWI controller. | |

RTC clock source identifiers | |

| #define | SYSCLK_RTCSRC_ULP CLK_RTCSRC_ULP_gc |

| #define | SYSCLK_RTCSRC_TOSC CLK_RTCSRC_TOSC_gc |

| #define | SYSCLK_RTCSRC_RCOSC CLK_RTCSRC_RCOSC_gc |

| #define | SYSCLK_RTCSRC_TOSC32 CLK_RTCSRC_TOSC32_gc |

| #define | SYSCLK_RTCSRC_RCOSC32 CLK_RTCSRC_RCOSC32_gc |

| #define | SYSCLK_RTCSRC_EXTCLK CLK_RTCSRC_EXTCLK_gc |

Aufzählungen | |

System Clock Port Numbers | |

| enum | sysclk_port_id { SYSCLK_PORT_GEN, SYSCLK_PORT_A, SYSCLK_PORT_B, SYSCLK_PORT_C, SYSCLK_PORT_D, SYSCLK_PORT_E, SYSCLK_PORT_F } |

Funktionen | |

Querying the system clock and its derived clocks | |

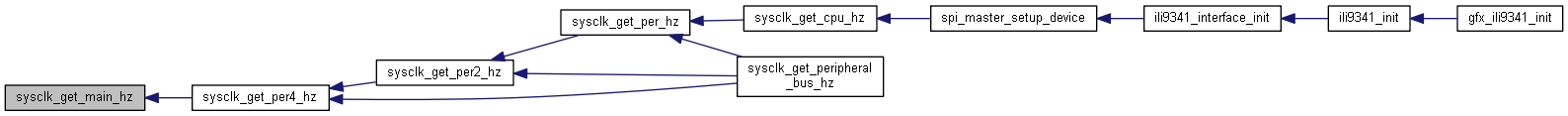

| static uint32_t | sysclk_get_main_hz (void) |

| Return the current rate in Hz of the main system clock. Mehr ... | |

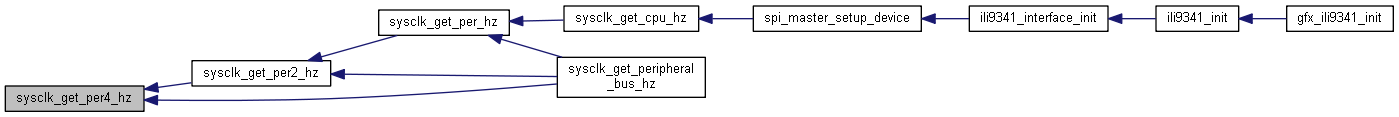

| static uint32_t | sysclk_get_per4_hz (void) |

| Return the current rate in Hz of clk_PER4. Mehr ... | |

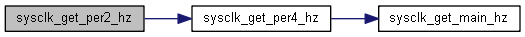

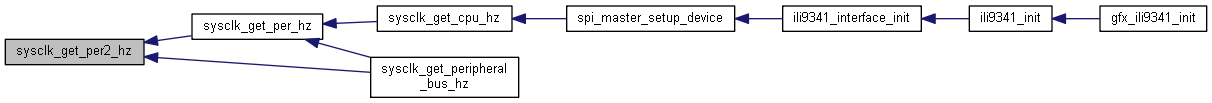

| static uint32_t | sysclk_get_per2_hz (void) |

| Return the current rate in Hz of clk_PER2. Mehr ... | |

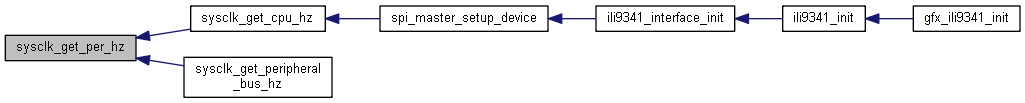

| static uint32_t | sysclk_get_per_hz (void) |

| Return the current rate in Hz of clk_PER. Mehr ... | |

| static uint32_t | sysclk_get_cpu_hz (void) |

| Return the current rate in Hz of the CPU clock. Mehr ... | |

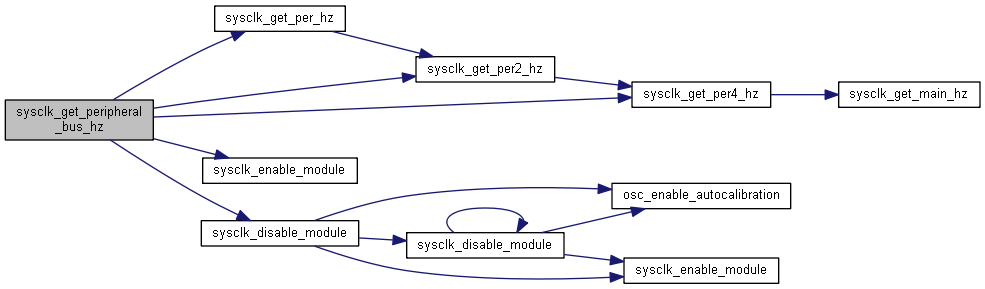

| static uint32_t | sysclk_get_peripheral_bus_hz (const volatile void *module) |

| Retrieves the current rate in Hz of the Peripheral Bus clock attached to the specified peripheral. Mehr ... | |

Enabling and disabling synchronous clocks | |

| void | sysclk_enable_module (enum sysclk_port_id port, uint8_t id) |

| Enable the clock to peripheral id on port port. Mehr ... | |

| void | sysclk_disable_module (enum sysclk_port_id port, uint8_t id) |

| Disable the clock to peripheral id on port port. Mehr ... | |

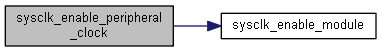

| static void | sysclk_enable_peripheral_clock (const volatile void *module) |

| Enable a peripheral's clock from its base address. Mehr ... | |

| static void | sysclk_disable_peripheral_clock (const volatile void *module) |

| Disable a peripheral's clock from its base address. Mehr ... | |

| static bool | sysclk_module_is_enabled (enum sysclk_port_id port, uint8_t id) |

| Check if the synchronous clock is enabled for a module. Mehr ... | |

System Clock Source and Prescaler configuration | |

| static void | sysclk_set_prescalers (uint8_t psadiv, uint8_t psbcdiv) |

| Set system clock prescaler configuration. Mehr ... | |

| static void | sysclk_set_source (uint8_t src) |

| Change the source of the main system clock. Mehr ... | |

| static void | sysclk_lock (void) |

| Lock the system clock configuration. Mehr ... | |

RTC clock source control | |

| static void | sysclk_rtcsrc_enable (uint8_t id) |

| Enable RTC clock with specified clock source. Mehr ... | |

| static void | sysclk_rtcsrc_disable (void) |

| Disable RTC clock. | |

System Clock Initialization | |

| void | sysclk_init (void) |

Chip-specific system clock management functions.

Copyright (c) 2010-2015 Atmel Corporation. All rights reserved.

Definiert in Datei sysclk.h.

| #define SYSCLK_RTCSRC_EXTCLK CLK_RTCSRC_EXTCLK_gc |

| #define SYSCLK_RTCSRC_RCOSC CLK_RTCSRC_RCOSC_gc |

| #define SYSCLK_RTCSRC_RCOSC32 CLK_RTCSRC_RCOSC32_gc |

| #define SYSCLK_RTCSRC_TOSC CLK_RTCSRC_TOSC_gc |

| #define SYSCLK_RTCSRC_TOSC32 CLK_RTCSRC_TOSC32_gc |

| #define SYSCLK_RTCSRC_ULP CLK_RTCSRC_ULP_gc |

| enum sysclk_port_id |

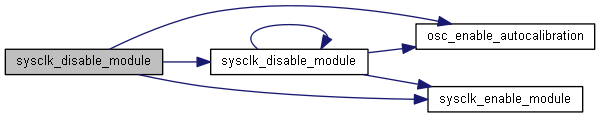

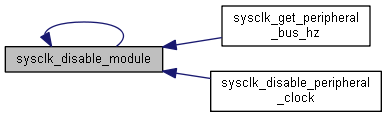

| void sysclk_disable_module | ( | enum sysclk_port_id | port, |

| uint8_t | id | ||

| ) |

Disable the clock to peripheral id on port port.

| port | ID of the port to which the module is connected (one of the SYSCLK_PORT_* definitions). |

| id | The ID (bitmask) of the peripheral module to be disabled. |

Definiert in Zeile 185 der Datei sysclk.c.

|

inlinestatic |

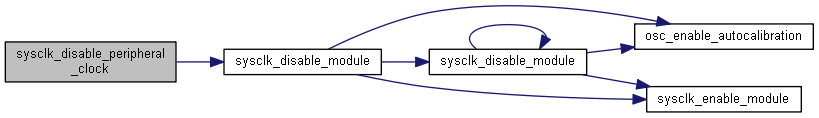

Disable a peripheral's clock from its base address.

Disables the clock to a peripheral, given its base address. If the peripheral has an associated clock on the HSB bus, this will be disabled also.

| module | Pointer to the module's base address. |

Definiert in Zeile 896 der Datei sysclk.h.

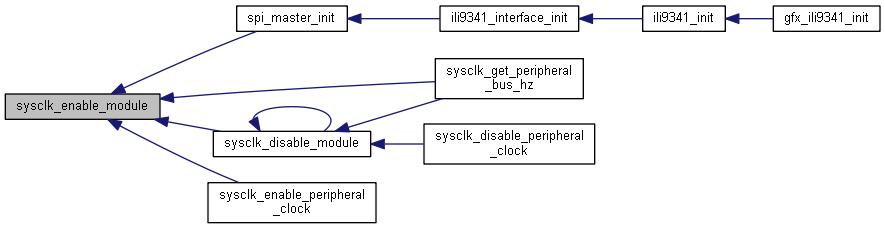

| void sysclk_enable_module | ( | enum sysclk_port_id | port, |

| uint8_t | id | ||

| ) |

Enable the clock to peripheral id on port port.

| port | ID of the port to which the module is connected (one of the SYSCLK_PORT_* definitions). |

| id | The ID (bitmask) of the peripheral module to be enabled. |

Definiert in Zeile 176 der Datei sysclk.c.

|

inlinestatic |

Enable a peripheral's clock from its base address.

Enables the clock to a peripheral, given its base address. If the peripheral has an associated clock on the HSB bus, this will be enabled also.

| module | Pointer to the module's base address. |

Definiert in Zeile 650 der Datei sysclk.h.

|

inlinestatic |

|

inlinestatic |

Return the current rate in Hz of the main system clock.

once it's been set up, and that PLL0 always runs at the compile-time configured default rate. While this is probably the most common configuration, which we want to support as a special case for performance reasons, we will at some point need to support more dynamic setups as well.

Definiert in Zeile 241 der Datei sysclk.h.

|

inlinestatic |

Return the current rate in Hz of clk_PER2.

This clock can run up to two times faster than the CPU clock.

Definiert in Zeile 316 der Datei sysclk.h.

|

inlinestatic |

Return the current rate in Hz of clk_PER4.

This clock can run up to four times faster than the CPU clock.

Definiert in Zeile 279 der Datei sysclk.h.

|

inlinestatic |

Return the current rate in Hz of clk_PER.

This clock always runs at the same rate as the CPU clock unless the divider is set.

Definiert in Zeile 343 der Datei sysclk.h.

|

inlinestatic |

Retrieves the current rate in Hz of the Peripheral Bus clock attached to the specified peripheral.

| module | Pointer to the module's base address. |

Definiert in Zeile 369 der Datei sysclk.h.

|

inlinestatic |

|

inlinestatic |

Check if the synchronous clock is enabled for a module.

| port | ID of the port to which the module is connected (one of the SYSCLK_PORT_* definitions). |

| id | The ID (bitmask) of the peripheral module to check (one of the SYSCLK_* module definitions). |

| true | If the clock for module id on port is enabled. |

| false | If the clock for module id on port is disabled. |

|

inlinestatic |

|

inlinestatic |

Set system clock prescaler configuration.

This function will change the system clock prescaler configuration to match the parameters.

| psadiv | The prescaler A setting (one of the SYSCLK_PSADIV_* definitions). This determines the clkPER4 frequency. |

| psbcdiv | The prescaler B and C settings (one of the SYSCLK_PSBCDIV_* definitions). These determine the clkPER2, clkPER and clkCPU frequencies. |

|